一种频率自适应欠采样电路的设计及FPGA 实现

裴永浩,苏淑靖*

(1.中北大学电子测试技术重点实验室,山西 太原030051;2.中北大学仪器科学与动态测试教育部重点实验室,山西太原030051)

欠采样多用于对高于奈奎斯特频率的信号进行数据采集的应用。 根据奈奎斯特-香农采样定理,在使用带通滤波器限制数据采集系统带宽,并且在已知数据采集系统的奈奎斯特频率和目标信号带宽的前提下,可以对此种特殊情况下的目标信号进行重构,而不会造成信息损失。 对于主要关注目标信号相位和幅值的相关应用,逐次逼近寄存器(Successive Approximation Register,SAR)型ADC 采样系统可配置为欠采样来实现系统性能目标。

在应用于高精度时基校准器的数字式锁相环结构中,锁相环参考时钟输入由欠采样下对时基信号的量化结果输出提供,ADC 采样时钟由锁相环输出提供,因此面临锁相环锁定前采样时钟的动态变化问题。 为解决信号采集系统欠采样频率动态变化的问题,设计提出一种能够自适应动态采样频率的欠采样数据采集系统,通过FPGA 对ADC 芯片进行精确时序控制,可实现对时基信号的自适应频率采样,有效保证了锁相环稳定的参考时钟输入。

1 对时基信号的欠采样

在数字锁相环中,被采时基信号源为恒温晶体振荡(OCXO),输出波形为10 MHz 正弦波,频率稳定性为±1.00 ppb(1 ppb =10-9),负载为50 Ω 情况下,温度变化速度小于2 ℃/min,可为时基校准系统提供稳定精准的时基信号输入。 时基信号的输出被欠采样保持电路欠采样,然后通过ADC 量化到数字域。

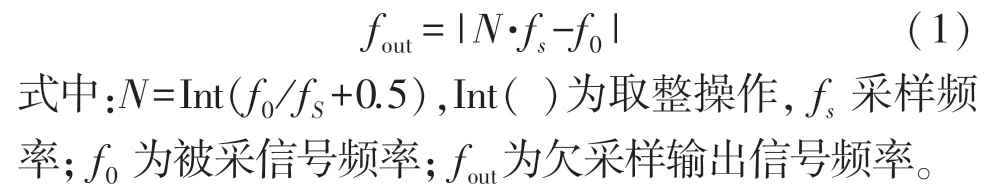

根据奈奎斯特采样定理,对于频率为f0的周期性信号,采样频率需满足fs>2f0。 然而在欠采样条件下, fs<2f0,采样频率与通带发生的混叠使得采样数据中被叠加进入多种频率的谐波成分,此时采集产生信号的频率即为混叠频率。 通过计算混叠频率fout可确定欠采样后采集信号的时域状态,根据混叠机理及混叠频率计算公式,确定欠采样后输出信号频率为:

2 信号采集硬件电路设计

2.1 总体设计结构

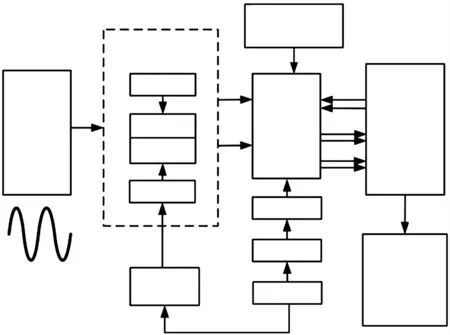

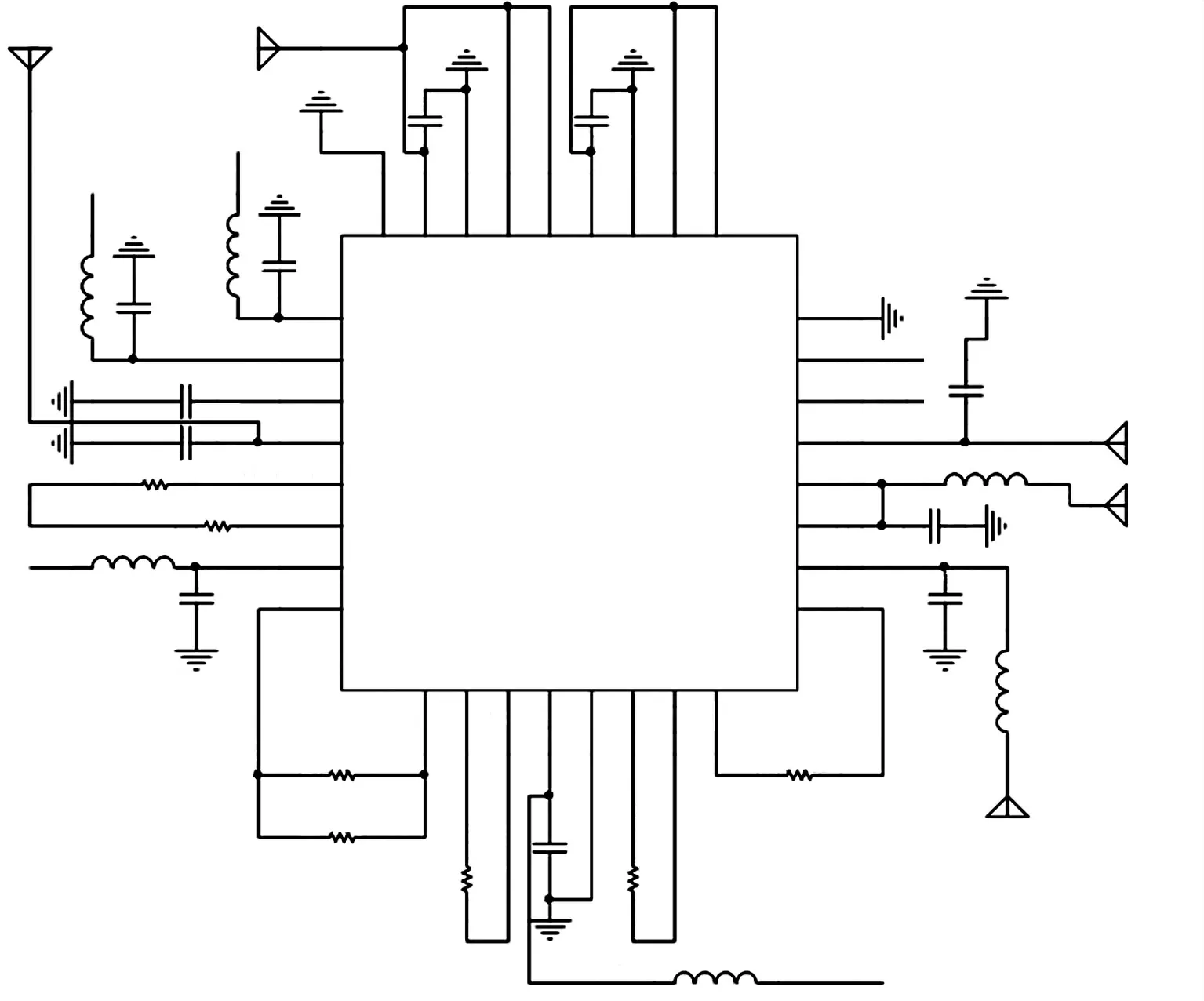

采样系统的总体结构主要由FPGA 控制单元、A/D 转换单元、电源、高速差分放大电路及OCXO 时基源构成,如图1 所示。 高速差分放大电路将10 MHz 标准信号转换至差分输出,FPGA 产生时序控制信号CLK±,AD7626 接收时序控制信号后,产生回波时钟DCO±,FPGA 根据回波时钟依次读取ADC 返回的串行数据D±。 FPGA 采用Xillix 公司的AIRTIX-7系列XC7A100T 芯片,适合高速数据通信和高速数据采集等应用,可以很好地满足欠采样时序控制需求。

图1 系统设计方案框图

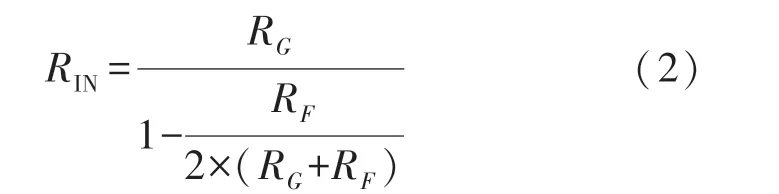

2.2 单端转差分信号驱动电路设计

设计所使用的单端转差分放大电路如图2 所示。使用差分运放驱动ADC,信号源之后配置的带通滤波器以抑制谐波。 信号源的特性阻抗为50 Ω,通过带通滤波器交流耦合到ADA4932,将信号源施加于ADA4932-1 的正输入时,要求信号源也以50 Ω 正确端接。 选中端接电阻R2,以使R2与ADA4932 输入阻抗的并联组合等于50 Ω。 ADA4932 输入阻抗RIN计算公式如下:

图2 ADA4932 驱动AD7626 电路

式中:RG=R3=R5,RF=R6=R7。 该差分驱动电路的配置增益为1,但基于50 Ω 信号源和ADA4932 输入端匹配的端阻抗的作用,相对于戴维南等效信号源电压,通道的净总增益约为0.5。

通过配置为单位增益缓冲器的运放AD8031 来缓冲AD7626 的VCM 输出电压,完成输出共模电压的设定。 在电路中,对应于4.096 V 的内部基准电压,AD7626 的输出共模电压为2.048 V,输入(IN+、IN-)在0 和+4.096 V 之间摆幅,发生180°反相。

2.3 A/D 转换电路设计

被采时基信号频率为10 MHz,数字锁相环前端需要以6 MHz~10 MHz 的动态变化采样频率对时基信号进行欠采样。 本文选用Analog Devices 公司的AD7626 作为模数转换芯片,AD7626 有着10 MHz的采样率、16 位数字信号输出和精准的内部参考电压,能够满足系统对采样率及分辨率的要求。AD7626 的典型配置连接电路如图3 所示,AD7626所接收的2.5V-LVDS 格式CNV 信号,由外部采样时钟驱动,配置可选择采用内部4.096 V 基准电压,差分信号CNV、D、DCO 和CLK 为ADC 与FPGA 之间的时序交互及数据输入输出端口。

图3 AD7626 典型连接电路原理图

3 欠采样时序控制的FPGA 实现

3.1 FPGA 程序设计

ADC 的模数转换由CNV 信号控制,在其上升沿启动转换。 上电后产生的第一个转换结果为无效数据,随后转换结果有效。 回波时钟接口模式下时序配置图如图4 所示,AD7626 与FPGA 之间有三个LVDS引脚,其中时钟DCO 与数据时钟D 同步,锁存数据信号D 在DCO 的上升沿更新。 FPGA 应在DCO 的上升沿捕捉数据D,且须在下一转换阶段的tCLKL时间内产生16 个CLK 脉冲。 从tCLKL至tMSB时间,信号D 和DCO 置0,且CLK 脉冲沿之间为空闲低电平状态。

图4 回波时钟模式下接口时序图

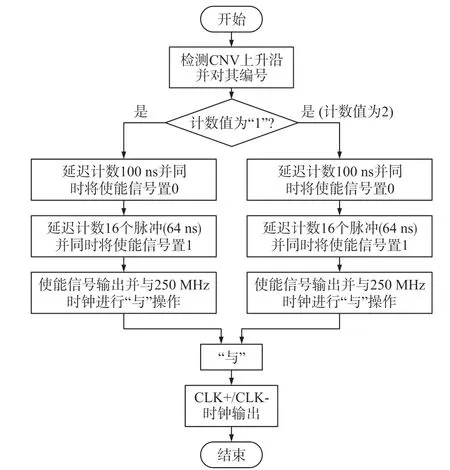

和同步时序逻辑设计方法相比,异步时序逻辑中,标志信号flag_2 在敏感信号CNV 的驱动下产生,而CLK 在系统时钟倍频信号(500 MHz)下驱动产生,因而此方法属于典型的异步时序逻辑,所使用FPGA 芯片在异步逻辑环境下,时钟最高运行至600 MHz,但在综合并布局布线之后,时序急剧恶化,建立时间裕量严重不足,时序仿真结果也表明,CLK时钟沿出现丢失或添加,时序状态也出现极大的紊乱,严重与ADC 时序要求不符,故需采用同步时序设计方式。 不论是同步时序逻辑的设计思想还是异步逻辑的设计方式,中心目的都是为了识别出转换驱动信号CNV 的上升沿,以适应CNV 信号频率的变化。 同步时序逻辑下CLK 时钟控制产生的程序流图如图5 所示。

图5 CLK±时钟产生控制流程图

3.2 时序逻辑设计

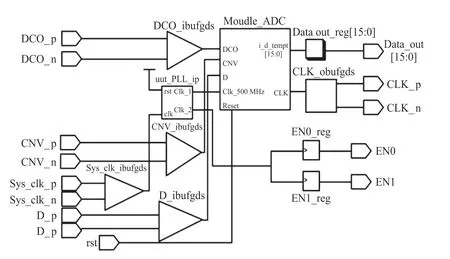

设计主要由iobufgds 缓冲单元、PLL 倍频/分频单元、Moudle_ADC 时序控制单元组成,如图6 所示。 其中ibufgds 和obufgds 单元分别将输入及输出进行差分至单端和单端至差分转换;PLL IP 核将系统时钟倍频至设计所需频率的时钟;时序主控模块在CNV 和系统时钟的驱动下进行时序配合和串行数据读取。

图6 采样时序控制FPGA 数字逻辑设计图

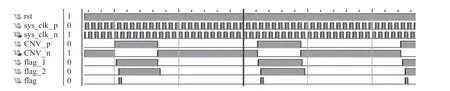

巧妙地利用FPGA 在进行寄存器值赋值过程中的时间差,将CNV 进行两次赋值操作:flag_1 <=CNV;flag_2<=flag_1;flag<=flag_1 &(~flag_2)。 取flag_2 信号的反信号与flag_1 信号做“与”,以得到CNV 识别状态信号flag(如图7 所示的脉冲沿)。

根据AD7626 芯片的工作要求:CNV 至D(MSB)就绪时间tMSB最大值为100 ns。 因此当tMSB小于100 ns 时,可能存在ADC 输出数据未完全就绪的情况。fCNV为9 MHz,设置tMSB的时间为33 ns,FPGA 采集回数据有误,DCO 返回波形为CLK 的包络;若硬性设置tMSB的时间为100 ns,则CNV 的一个周期内无法覆盖,中间会跳过一个上升沿(16 时钟沿必须持续输出完毕才能启动下一次识别),不符合时序要求;设置fCNV为5 MHz,此时设置就绪时间为105 ns,在线逻辑(ILA)分析显示返回的DCO 可见清晰的16 个时钟沿,但采集的16 位二进制数结果存在较大量化误差。fCLK的典型值为250 MHz,则16 个时钟沿所需消耗的时间至少为64 ns,加之至少100 ns 的就绪时间tMSB,大大超过了转换信号CNV 的周期111 ns,因此必然会存在ADC 手册时序图中所呈现的时序状态,而无法做到如5 MHz 采样率时的一个CNV 周期覆盖16个CLK 时钟沿的情况。

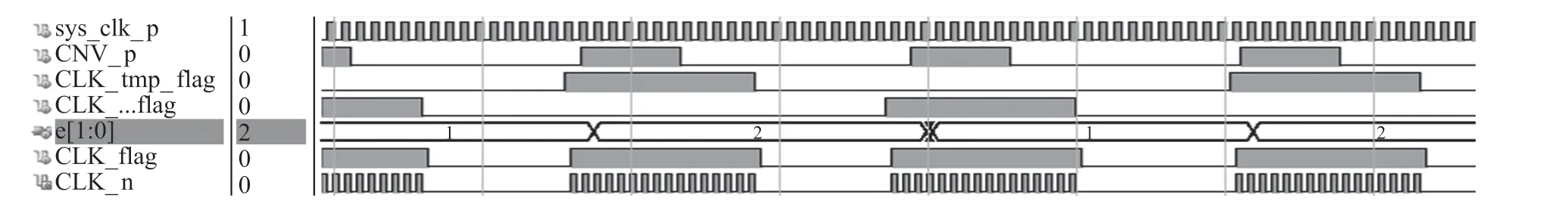

有效做法是两路做交替采样后,再进行数据拼接。 对CNV 转换信号进行计数并标号,当标号为“1”时进行第一路采集转换,当标号为“2”时进行第二路采集转换,如图8 所示,信号“e”为计数标志。 每当相应的计数标志来临,在选通信号“CLK_flag”下进行该通道的时钟信号输出,与此同时,启动更高速敏感信号(500 MHz)下的进程,将两路产生的CLK 信号进行拼接,由此产生满足ADC 时序要求的CLK 信号。

图8 同步时序逻辑CLK 信号产生状态图

图7 同步时序逻辑标志信号产生状态图

4 高速差分运放与A/D 结果测试分析

4.1 时基源与差分运放单元输出测试

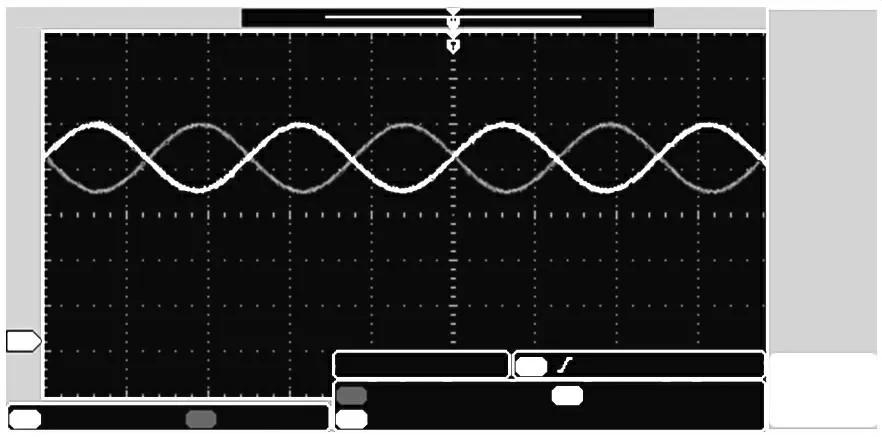

被采信号源恒温晶体振荡器(OCXO)在3.3 V 供电电压下,有高稳的10 MHz 正弦信号输出,如图9 所示。 单端转差分模块输出测试结果如图10 所示,转换输出信号成180°反相。 由于单端转差分模块差分放大实际增益配置约为0.43,故差分输出信号测量幅值为700 mV,共模电压2.04 V,均在AD7626 允许输出入范围。

图9 OCXO 时钟源10 MHz 正弦信号输出(a)

4.2 自适应频率欠采样输出结果测试

图10 单端至差分高速转换模块输出

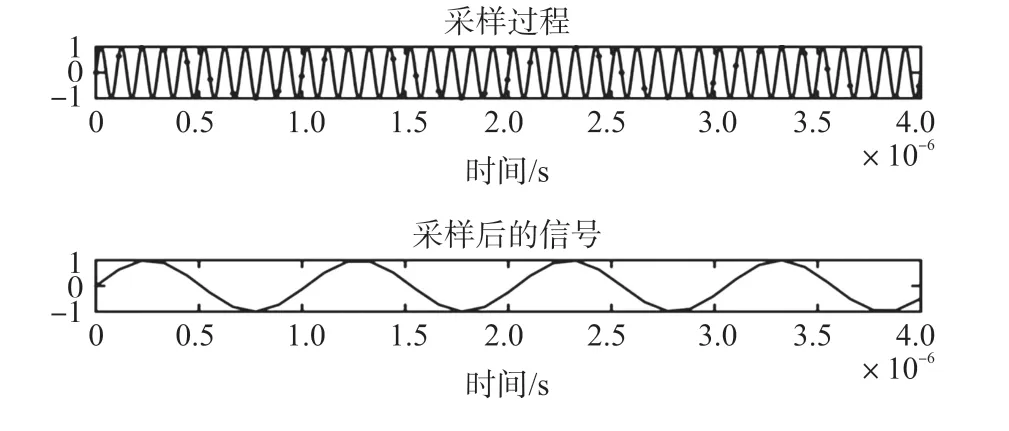

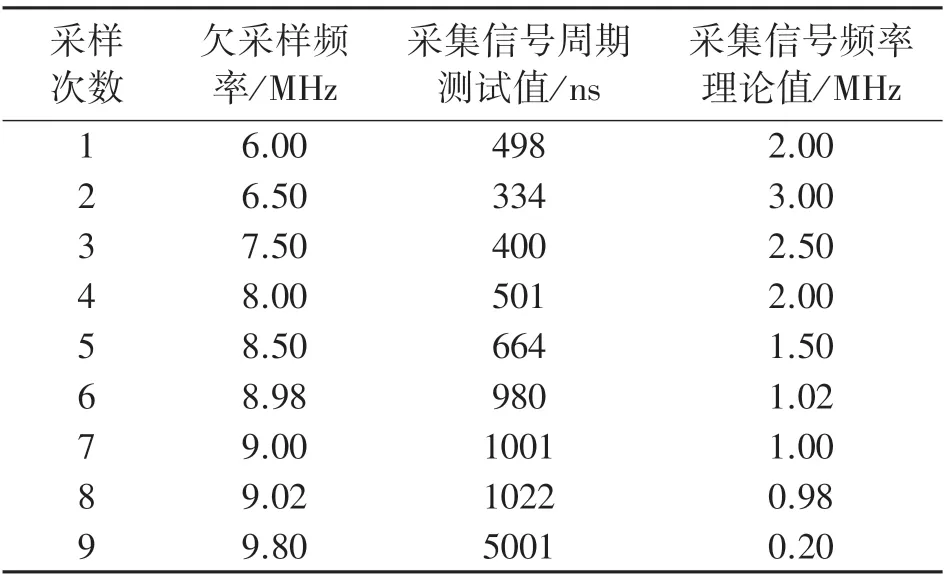

对波形数据的采集结果,可采用FPGA 内嵌逻辑分析仪ILA,在工程中添加相应的测试Probes,对16位数据(串行/并行)输出、AD7626 的回波时钟及串并转换使能信号enable_test 进行测试。 如图11 所示,Waveform-hw_ila 窗口中显示,DCO 时钟频率250 MHz,每隔16 个时钟沿有固定时间的低电平,D 为串行数据输出,在DCO 时钟的驱动下对串行数据D 进行读取并经串并转换后得到输出数据data_out[15:0],可对数据进行模拟化显示,如图12 得到时域平滑的正弦波形。 为进一步分析输出数据,将ILA 数据导出.csv 文件,通过MATLAB 对该文件进行读取并Plot,如图12 所示。 由于采样率较低,在原始信号时域内,一个周期内只能采集一个数据,可以看出波形周期为1 μs(1 MHz),在一个周期内的采样点数为9点,符合欠采样理论。 锁相环频率输出由码型信号发生器81131A 代替,改变转换驱动信号CNV 的频率(采样频率),对采集波形进行抓取。 在不同采样率下对波形周期进行测量,汇总结果如表1 所示,其周期值较理论值在容许误差范围内。

图11 FPGA 内嵌逻辑分析仪(ILA)对采集信号的抓取结果(采样率9 MHz)

图12 欠采样过程的Plot 结果(采样率9 MHz)

表1 自适应采样率下采集输出测试表

5 总结

本文利用FPGA 对AD7626 进行时序控制,根据AD7626 所接收的频率变化的转换驱动信号CNV,对输入信号进行自适应采样频率的数据采集,通过FPGA 内嵌逻辑分析仪对采集数据进行频率分析,切合了理论结果。 设计充分利用了欠采样技术的特点,能够动态适应采样频率的变化,在有效获取高稳时基源信号信息的同时,降低了信号采集系统的带宽要求,能够满足高精度时基校准器的要求,具有一定的工程应用价值。